# **Trusted Firmware-A Tests**

unknown

# **CONTENTS**

| 1 | About                      | 1  |

|---|----------------------------|----|

| 2 | Getting Started            | 5  |

| 3 | Processes & Policies       | 17 |

| 4 | Framework Design           | 19 |

| 5 | Implementing Tests         | 23 |

| 6 | Porting                    | 25 |

| 7 | Change Log & Release Notes | 33 |

| 8 | License                    | 59 |

| 9 | Getting started            | 61 |

**CHAPTER**

ONE

### **ABOUT**

# 1.1 Feature Overview

This page provides an overview of the current TF-A Tests feature set. The *Change Log & Release Notes* document provides details of changes made since the last release.

#### 1.1.1 Current Features

The following TF-A features are currently tested to some extent (this list is not exhaustive):

- SMC Calling Convention

- Power State Coordination Interface (PSCI)

- Software Delegated Exception Interface (SDEI)

- Performance Measurement Framework (PMF)

- Communication and interaction with the Test Secure Payload (TSP)

- Firmware update (or recovery mode)

- EL3 payload boot flow

- Secure partition support

- True Random Number Generator Firmware Interface (TRNG\_FW)

These tests are not a compliance test suite for the Arm interface standards used in TF-A (such as PSCI).

They do not cover 100% of the TF-A code. The fact that all tests pass does not mean that TF-A is free of bugs.

They are not reference code. They should not be considered as the official way to test hardware/firmware features. Instead, they are provided as example code to experiment with and improve on.

#### 1.1.2 Still to come

- · Additional tests

- Support for new platforms

- Design improvements

- Stability improvements

- Enhancements to the test framework to make it easier to implement tests

- Fixes for known issues (detailed in Change Log & Release Notes)

Copyright (c) 2019-2023, Arm Limited. All rights reserved.

# 1.2 Platform Support

# 1.2.1 Juno Arm Development Platform

The AArch64 build of this release has been tested on variants r0, r1 and r2 of the *Juno Arm Development Platform*. The AArch32 build has only been tested on variant r0.

### 1.2.2 Army8 Architecture Fixed Virtual Platforms

The AArch64 build has been tested on the following Armv8 Architecture Fixed Virtual Platforms (FVP):

- FVP\_Base\_AEMv8A-AEMv8A

- FVP\_Base\_Cortex-A35x4

- FVP\_Base\_Cortex-A57x4-A53x4

- FVP\_Base\_RevC-2xAEMv8A

- Foundation\_Platform

The AArch32 build has been tested on the following FVPs:

- FVP\_Base\_Cortex-A32x4

- FVP\_Base\_RevC-2xAEMv8A

NOTE: Unless otherwise stated, the model version is version 11.6, build 45.

# 1.2.3 System Guidance for Infrastructure (SGI) Fixed Virtual Platforms

The AArch64 build has been tested on the following Fixed Virtual Platforms (FVP):

- FVP\_CSS\_SGI-575

- FVP\_RD\_N1Edge

#### NOTE:

• For FVP\_CSS\_SGI-575 and FVP\_RD\_N1Edge, internal version of the models were used.

Copyright (c) 2019, Arm Limited. All rights reserved.

2 Chapter 1. About

# 1.3 Maintainers

Trusted Firmware-A Tests (TF-A Tests) is a community maintained project. All contributions are ultimately merged by the maintainers listed below.

Please note the maintainers' bandwidth is limited and contributions to this project will be reviewed and handled on a best-effort basis.

#### 1.3.1 Maintainers List

- Alexei Fedorov <alexei.fedorov@arm.com>

- Bipin Ravi <br/>

<br/>bipin.ravi@arm.com>

- Dan Handley <dan.handley@arm.com>

- Joanna Farley <joanna.farley@arm.com>

- Manish Pandey <manish.pandey2@arm.com>

- Mark Dykes <mark.dykes@arm.com>

- Olivier Deprez <olivier.deprez@arm.com>

- Sandrine Bailleux <sandrine.bailleux@arm.com>

- Soby Mathew <soby.mathew@arm.com>

Copyright (c) 2018-2020, Arm Limited. All rights reserved.

# 1.4 Support & Contact

We welcome any feedback on TF-A Tests and there are several methods for providing it or for obtaining support.

# 1.4.1 Mailing Lists

Public mailing lists for TF-A Tests and the wider Trusted Firmware project are hosted on TrustedFirmware.org. The mailing lists can be used for general enquiries, enhancement requests and issue reports, or to follow and participate in technical or organizational discussions around the project. These discussions include design proposals, advance notice of changes and upcoming events.

The relevant list for the TF-A Tests project is TF-A-Tests development

You can see a summary of all the lists on the TrustedFirmware.org website.

1.3. Maintainers 3

# 1.4.2 Issue Tracker

Specific issues may be raised using the issue tracker on the TrustedFirmware.org website. Using this tracker makes it easy for the maintainers to prioritise and respond to your ticket.

Copyright (c) 2019-2022, Arm Limited. All rights reserved.

Copyright (c) 2019, Arm Limited. All rights reserved.

Chapter 1. About

**CHAPTER**

**TWO**

# **GETTING STARTED**

# 2.1 Prerequisites & Requirements

This document describes the software and hardware requiremnts for building TF-A Tests for AArch32 and AArch64 target platforms.

It may be possible to build TF-A Tests with combinations of software and hardware that are different from those listed below. The software and hardware described in this document are officially supported.

#### 2.1.1 Build Host

TF-A Tests may be built using a Linux build host machine with a recent Linux distribution. We have performed tests using Ubuntu 22.04 LTS (64-bit), but other distributions should also work fine, provided that the tools and libraries can be installed.

#### 2.1.2 Toolchain

Install the required packages to build TF-A Tests with the following command:

sudo apt-get install device-tree-compiler build-essential git perl libxml-libxml-perl

Download and install the GNU cross-toolchain from Arm. The TF-A Tests have been tested with version 12.2.Rel1 (gcc 12.2):

• GCC cross-toolchain

In addition, the following optional packages and tools may be needed:

• For debugging, Arm Development Studio (Arm-DS).

Copyright (c) 2019-2022, Arm Limited. All rights reserved.

# 2.2 Building Documentation

To create a rendered copy of this documentation locally you can use the Sphinx tool to build and package the plain-text documents into HTML-formatted pages.

If you are building the documentation for the first time then you will need to check that you have the required software packages, as described in the *Prerequisites* section that follows.

**Note:** An online copy of the documentation is available at https://trustedfirmware-a-tests.readthedocs.io, if you want to view a rendered copy without doing a local build.

# 2.2.1 Prerequisites

For building a local copy of the documentation you will need, at minimum:

- Python 3 (3.5 or later)

- PlantUML (1.2017.15 or later)

You must also install the Python modules that are specified in the requirements.txt file in the root of the docs directory. These modules can be installed using pip3 (the Python Package Installer). Passing this requirements file as an argument to pip3 automatically installs the specific module versions required by TF-A Tests.

An example set of installation commands for Ubuntu 18.04 LTS follows, assuming that the working directory is docs:

```

sudo apt install python3 python3-pip plantuml

pip3 install [--user] -r requirements.txt

```

**Note:** Several other modules will be installed as dependencies. Please review the list to ensure that there will be no conflicts with other modules already installed in your environment.

Passing the optional --user argument to pip3 will install the Python packages only for the current user. Omitting this argument will attempt to install the packages globally and this will likely require the command to be run as root or using sudo.

**Note:** More advanced usage instructions for *pip* are beyond the scope of this document but you can refer to the pip homepage for detailed guides.

# 2.2.2 Building rendered documentation

The documentation can be built into HTML-formatted pages from the project's root directory by running the following command.

make doc

Output from the build process will be placed in:

docs/build/html

We also support building documentation in other formats. From the docs directory of the project, run the following command to see the supported formats. It is important to note that you will not get the correct result if the command is run from the project's root directory, as that would invoke the top-level Makefile for TF-A Tests themselves.

```

make help

```

# 2.2.3 Building rendered documentation from a container

There may be cases where you can not either install or upgrade required dependencies to generate the documents, so in this case, one way to create the documentation is through a docker container. The first step is to check if docker is installed in your host, otherwise check main docker page for installation instructions. Once installed, run the following script from project root directory

```

docker run --rm -v $PWD:/TF sphinxdoc/sphinx \

bash -c 'cd /TF && \

pip3 install plantuml -r ./docs/requirements.txt && make doc'

```

The above command fetches the sphinxdoc/sphinx container from docker hub, launches the container, installs documentation requirements and finally creates the documentation. Once done, exit the container and output from the build process will be placed in:

```

docs/build/html

```

Copyright (c) 2020, Arm Limited. All rights reserved.

# 2.3 Obtaining Source Code

Download the TF-A Tests source code using the following command:

```

git clone https://git.trustedfirmware.org/TF-A/tf-a-tests.git

```

Copyright (c) 2019, Arm Limited. All rights reserved.

# 2.4 Building TF-A Tests

• Before building TF-A Tests, the environment variable CROSS\_COMPILE must point to the cross compiler.

For AArch64:

```

export CROSS_COMPILE=<path-to-aarch64-gcc>/bin/aarch64-none-elf-

```

For AArch32:

```

export CROSS_COMPILE=<path-to-aarch32-gcc>/bin/arm-eabi-

```

• Change to the root directory of the TF-A Tests source tree and build.

For AArch64:

make PLAT=<platform>

For AArch32:

make PLAT=<platform> ARCH=aarch32

#### Notes:

- If PLAT is not specified, fvp is assumed by default. See the TF-A documentation for more information on available build options.

- By default this produces a release version of the build. To produce a debug version instead, build the code with DEBUG=1.

- The build process creates products in a build/ directory tree, building the objects and binaries for each

test image in separate sub-directories. The following binary files are created from the corresponding ELF

files:

- \* build/<platform>/<build-type>/tftf.bin

- \* build/<platform>/<build-type>/ns\_bl1u.bin

- \* build/<platform>/<build-type>/ns\_bl2u.bin

- \* build/<platform>/<build-type>/el3\_payload.bin

- \* build/<platform>/<build-type>/cactus\_mm.bin

- \* build/<platform>/<build-type>/cactus.bin

- \* build/<platform>/<build-type>/ivy.bin

where <platform> is the name of the chosen platform and <build-type> is either debug or release. The actual number of images might differ depending on the platform.

Refer to the sections below for more information about each image.

• Build products for a specific build variant can be removed using:

```

make DEBUG=<D> PLAT=<platform> clean

```

... where <D> is 0 or 1, as specified when building.

The build tree can be removed completely using:

#### make realclean

• Use the following command to list all supported build commands:

make help

# 2.4.1 TFTF test image

tftf.bin is the main test image to exercise the TF-A features. The other test images provided in this repository are optional dependencies that TFTF needs to test some specific features.

tftf.bin may be built independently of the other test images using the following command:

```

make PLAT=<platform> tftf

```

In TF-A boot flow, tftf.bin replaces the BL33 image and should be injected in the FIP image. This might be achieved by running the following command from the TF-A root directory:

```

BL33=<path/to/tftf.bin> make PLAT=<platform> fip

```

Please refer to the TF-A documentation for further details.

# 2.4.2 Realm payload test image

realm.bin is the realm payload test image and is packaged along with tftf for Realm Management Extension (RME) testing. This can be built using the following command:

```

make PLAT=<platform> realm

```

The generated realm.bin needs to be packaged as part of tftf.bin to be used as a single BL33 image and can be done using the following command:

```

make PLAT=<platform> pack_realm

```

Please refer to the TF-A RME documentation for build and run instructions.

### 2.4.3 NS BL1U and NS BL2U test images

$ns_bl1u.bin$  and  $ns_bl2u.bin$  are test images that exercise the *Firmware Update (FWU)* feature of TF-A<sup>1</sup>. Throughout this document, they will be referred as the *FWU test images*.

In addition to updating the firmware, the FWU test images also embed some tests that exercise the FWU state machine implemented in the TF-A. They send valid and invalid SMC requests to the TF-A BL1 image in order to test its robustness.

#### NS BL1U test image

The NS\_BL1U image acts as the *Application Processor (AP) Firmware Update Boot ROM*. This typically is the first software agent executing on the AP in the Normal World during a firmware update operation. Its primary purpose is to load subsequent firmware update images from an external interface, such as NOR Flash, and communicate with BL1 to authenticate those images.

The NS\_BL1U test image provided in this repository performs the following tasks:

- Load FWU images from external non-volatile storage (typically flash memory) to Non-Secure RAM.

- Request TF-A BL1 to copy these images in Secure RAM and authenticate them.

- Jump to NS\_BL2U which carries out the next steps in the firmware update process.

<sup>&</sup>lt;sup>1</sup> Therefore, the Trusted Board Boot feature must be enabled in TF-A for the FWU test images to work. Please refer the TF-A documentation for further details.

This image may be built independently of the other test images using the following command:

make PLAT=<platform> ns\_bl1u

#### NS BL2U test image

The NS\_BL2U image acts as the *AP Firmware Updater*. Its primary responsibility is to load a new set of firmware images from an external interface and write them into non-volatile storage.

The NS\_BL2U test image provided in this repository overrides the original FIP image stored in flash with the backup FIP image (see below).

This image may be built independently of the other test images using the following command:

make PLAT=<platform> ns\_bl2u

### Putting it all together

The FWU test images should be used in conjunction with the TFTF image, as the latter initiates the FWU process by corrupting the FIP image and resetting the target. Once the FWU process is complete, TFTF takes over again and checks that the firmware was successfully updated.

To sum up, 3 images must be built out of the TF-A Tests repository in order to test the TF-A Firmware Update feature:

- ns\_bl1u.bin

- ns\_bl2u.bin

- tftf.bin

Once that's done, they must be combined in the right way.

- ns\_bl1u.bin is a standalone image and does not require any further processing.

- ns\_bl2u.bin must be injected into the FWU\_FIP image. This might be achieved by setting NS\_BL2U=ns\_bl2u. bin when building the FWU\_FIP image out of the TF-A repository. Please refer to the section Building FIP images with support for Trusted Board Boot in the TF-A documentation.

- tftf.bin must be injected in the standard FIP image, as explained in section TFTF test image.

Additionally, on Juno platform, the FWU FIP must contain a SCP\_BL2U image. This image can simply be a copy of the standard SCP\_BL2 image if no specific firmware update operations need to be carried on the SCP side.

Finally, the backup FIP image must be created. This can simply be a copy of the standard FIP image, which means that the Firmware Update process will restore the original, uncorrupted FIP image.

# 2.4.4 EL3 test payload

el3\_payload.bin is a test image exercising the alternative EL3 payload boot flow in TF-A. Refer to the EL3 test payload README file for more details about its behaviour and how to build and run it.

### 2.4.5 SPM test images

This repository contains three sample Secure Partitions (SP) meant to be used with one implementation of a Secure Partition Manager (SPM):

- · Cactus-MM

- · Cactus and Ivy

They are only supported on AArch64 FVP. They can be built independently of the other test images using the following command:

```

make PLAT=fvp cactus ivy cactus_mm

```

To run the full set of tests in the Secure Partitions, they should be used in conjunction with the TFTF image.

Please refer to the TF-A documentation for further details.

#### Cactus-MM

Cactus-MM is designed to test the TF-A EL3 SPM implementation (TF-A Secure Partition Manager (MM)) based on the Arm Management Mode Interface (MM)

This SP runs in Secure-EL0 and performs the following tasks:

- Test that TF-A has correctly setup the secure partition environment: it should be allowed to perform cache maintenance operations, access floating point registers, etc.

- Test that TF-A accepts to change data access permissions and instruction permissions on behalf of the Secure Partition for memory regions the latter owns.

- Test communication with SPM through MM interface.

In the TF-A boot flow, the partition replaces the BL32 image and should be injected in the FIP image. To test SPM-MM with Cactus-MM, it is enough to use cactus\_mm.bin as BL32 image.

For SPM-MM, build TF-A following Building TF-A Secure Partition Manager (MM) and the following commands can be used to build the tests:

```

# TF-A-Tests repository:

make PLAT=fvp TESTS=spm-mm tftf cactus_mm

```

#### Cactus and Ivy

Cactus and Ivy are designed to test the FF-A based SPM implementation with secure virtualization enabled. Refer to Arm Firmware Framework for Armv8-A

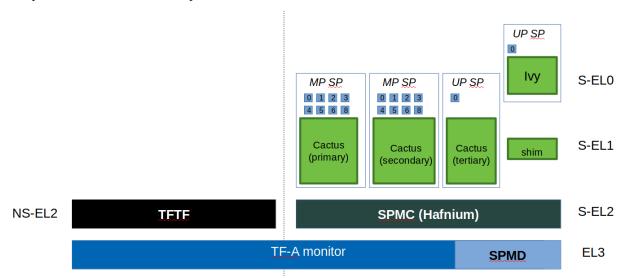

In the TF-A reference code base, BL31 implements the SPMD and BL32 the SPMC. The SPMC runs at S-EL2 and acts as a partition manager for multiple secure partitions (TF-A Secure Partition Manager (FF-A)):

• Cactus is a sample FF-A compliant S-EL1 partition. As a matter of providing a realistic test harness, three instances of the same partition binary are launched as separate SPs (hence assigned three different FF-A IDs corresponding each to a different secure partition). Each secure partition instance has a separate manifest (Cactus sample manifest, Cactus secondary manifest, Cactus tertiary manifest). First two instances are MP SPs. Third instance is a UP SP. Each instance runs a set of built-in tests at boot time. They exercise SP to SPMC FF-A interfaces contained in the secure world. The partition interacts with the SPMC through SMC. Once the NWd and TFTF are started, another set of run-time tests exercise the normal world to secure world primitives.

• Ivy is a specific kind of S-EL1 UP partition, where the S-EL1 exception level consists of a thin shim layer. The applicative part of the partition is held at S-EL0. The shim provides early bootstrap code, MMU configuration and a vector table trapping S-EL0 requests. The application interacts with the shim through FF-A protocol by the use of SVC instruction. The shim relays the request to the SPMC by an SMC. The S-EL0 application doesn't require knowledge of the shim, and can be self contained.

This picture illustrates the test setup:

To build TFTF with SPM tests, Cactus and Ivy use:

```

# TF-A-Tests repository:

make PLAT=fvp TESTS=spm tftf cactus ivy

```

Copyright (c) 2019-2021, Arm Limited. All rights reserved.

# 2.5 Build Options Summary

As far as possible, TF-A Tests dynamically detects the platform hardware components and available features. There are a few build options to select specific features where the dynamic detection falls short.

Unless mentioned otherwise, these options are expected to be specified at the build command line and are not to be modified in any component makefiles.

**Note:** The build system doesn't track dependencies for build options. Therefore, if any of the build options are changed from a previous build, a clean build must be performed.

### 2.5.1 Common (Shared) Build Options

Most of the build options listed in this section apply to TFTF, the FWU test images and Cactus, unless otherwise specified. These do not influence the EL3 payload, whose simplistic build system is mostly independent.

- ARCH: Choose the target build architecture for TF-A Tests. It can take either aarch64 or aarch32 as values. By default, it is defined to aarch64. Not all test images support this build option.

- ARM\_ARCH\_FEATURE: Optional Arm Architecture build option which specifies one or more feature modifiers. This option has the form [no]feature+... and defaults to none. It translates into compiler option -march=armvX[.Y]-a+[no]feature+.... See compiler's documentation for the list of supported feature modifiers.

- ARM\_ARCH\_MAJOR: The major version of Arm Architecture to target when compiling TF-A Tests. Its value must be numeric, and defaults to 8.

- ARM\_ARCH\_MINOR: The minor version of Arm Architecture to target when compiling TF-A Tests. Its value must be a numeric, and defaults to 0.

- BRANCH\_PROTECTION: Numeric value to enable ARMv8.3 Pointer Authentication (ARMv8.3-PAuth) and ARMv8.5 Branch Target Identification (ARMv8.5-BTI) support in the Trusted Firmware-A Test Framework itself. If enabled, it is needed to use a compiler that supports the option -mbranch-protection (GCC 9 and later). Selects the branch protection features to use:

- 0: Default value turns off all types of branch protection

- 1: Enables all types of branch protection features

- 2: Return address signing to its standard level

- 3: Extend the signing to include leaf functions

- 4: Turn on branch target identification mechanism

The table below summarizes BRANCH\_PROTECTION values, GCC compilation options and resulting PAuth/BTI features.

| Value | GCC option   | PAuth | BTI |

|-------|--------------|-------|-----|

| 0     | none         | N     | N   |

| 1     | standard     | Y     | Y   |

| 2     | pac-ret      | Y     | N   |

| 3     | pac-ret+leaf | Y     | N   |

| 4     | bti          | N     | Y   |

This option defaults to 0 and this is an experimental feature.

- DEBUG: Chooses between a debug and a release build. A debug build typically embeds assertions checking the validity of some assumptions and its output is more verbose. The option can take either 0 (release) or 1 (debug) as values. 0 is the default.

- ENABLE\_ASSERTIONS: This option controls whether calls to assert() are compiled out.

- For debug builds, this option defaults to 1, and calls to assert() are compiled in.

- For release builds, this option defaults to 0 and calls to assert() are compiled out.

This option can be set independently of DEBUG. It can also be used to hide any auxiliary code that is only required for the assertion and does not fit in the assertion itself.

• LOG\_LEVEL: Chooses the log level, which controls the amount of console log output compiled into the build. This should be one of the following:

```

0 (LOG_LEVEL_NONE)

10 (LOG_LEVEL_ERROR)

20 (LOG_LEVEL_NOTICE)

30 (LOG_LEVEL_WARNING)

40 (LOG_LEVEL_INFO)

50 (LOG_LEVEL_VERBOSE)

```

All log output up to and including the selected log level is compiled into the build. The default value is 40 in debug builds and 20 in release builds.

- PLAT: Choose a platform to build TF-A Tests for. The chosen platform name must be a subdirectory of any depth under plat/, and must contain a platform makefile named platform.mk. For example, to build TF-A Tests for the Arm Juno board, select PLAT=juno.

- V: Verbose build. If assigned anything other than 0, the build commands are printed. Default is 0.

# 2.5.2 Arm FVP Platform Specific Build Options

- FVP\_CLUSTER\_COUNT: Configures the cluster count to be used to build the topology tree within TFTF. By default TFTF is configured for dual cluster for CPUs with single thread (ST) and single cluster for SMT CPUs. For ST CPUs this option can be used to override the default number of clusters with a value in the range 1-4.

- FVP\_MAX\_CPUS\_PER\_CLUSTER: Sets the maximum number of CPUs implemented in a single cluster. This option defaults to the maximum value of 4 for ST CPUs and maximum value of 8 for SMT CPUs.

- FVP\_MAX\_PE\_PER\_CPU: Sets the maximum number of PEs implemented on any CPU in the system. This option defaults to 1 to select ST CPUs. For platforms with SMT CPUs this value must be set to 2.

# 2.5.3 TFTF-specific Build Options

- NEW\_TEST\_SESSION: Choose whether a new test session should be started every time or whether the framework should determine whether a previous session was interrupted and resume it. It can take either 1 (always start new session) or 0 (resume session as appropriate). 1 is the default.

- TESTS: Set of tests to run. Use the following command to list all possible sets of tests:

```

make help_tests

```

If no set of tests is specified, the standard tests will be selected (see tftf/tests/tests-standard.xml).

• USE\_NVM: Used to select the location of test results. It can take either 0 (RAM) or 1 (non-volatile memory like flash) as test results storage. Default value is 0, as writing to the flash significantly slows tests down.

# 2.5.4 Realm payload specific Build Options

• TFTF\_MAX\_IMAGE\_SIZE: The option needs to be either set by the user or by the platform makefile to specify the maximum size of TFTF binary. This is needed so that the Realm payload binary can be appended to TFTF binary via make pack\_realm build command.

# 2.5.5 FWU-specific Build Options

• FIRMWARE\_UPDATE: Whether the Firmware Update test images (i.e. NS\_BL1U and NS\_BL2U) should be built. The default value is 0. The platform makefile is free to override this value if Firmware Update is supported on this platform.

Copyright (c) 2019-2020, Arm Limited. All rights reserved.

# 2.6 Running Tests

Refer to the Juno and FVP platform documentation in the *TF-A documentation*. The same instructions mostly apply to running the TF-A Tests on those two platforms. The difference is that the following images are not needed here:

- Normal World bootloader. The TFTF replaces it in the boot flow;

- Linux Kernel;

- Device tree;

- · Filesystem.

In other words, only the following software images are needed:

- BL1 firmware image;

- FIP image containing the following images:

- BL2;

- SCP\_BL2 if required by the platform (e.g. Juno);

- BL31;

- BL32 (optional);

- tftf.bin (standing as the BL33 image).

# 2.6.1 Running Manual Tests on FVP

The manual tests rely on storing state in non-volatile memory (NVM) across reboot. On FVP the NVM is not persistent across reboots, so the following flag must be used to write the NVM to a file when the model exits.

```

-C bp.flashloader0.fnameWrite=[filename]

```

To ensure the model exits on shutdown the following flag must be used:

```

-C bp.ve_sysregs.exit_on_shutdown=1

```

After the model has been shutdown, this file must be fed back in to continue the test. Note this flash file includes the FIP image, so the original fip.bin does not need to be passed in. The following flag is used:

```

-C bp.flashloader0.fname=[filename]

```

2.6. Running Tests 15

### 2.6.2 Running Firmware Update (FWU) Tests

As previously mentioned in *Putting it all together*, there are a couple of extra images involved when running the FWU tests. They need to be loaded at the right addresses, which depend on the platform.

#### On FVP

In addition to the usual BL1 and FIP images, the following extra images must be loaded:

- NS\_BL1U image at address 0x0BEB8000 (i.e. NS\_BL1U\_BASE macro in TF-A)

- FWU\_FIP image at address 0x08400000 (i.e. NS\_BL2U\_BASE macro in TF-A)

- Backup FIP image at address 0x09000000 (i.e. FIP\_BKP\_ADDRESS macro in TF-A tests).

An example script is provided in scripts/run\_fwu\_fvp.sh.

#### On Juno

The same set of extra images and load addresses apply for Juno as for FVP.

The new images must be programmed in flash memory by adding some entries in the SITE1/HBI0262x/images.txt configuration file on the Juno SD card (where x depends on the revision of the Juno board). Refer to the Juno Getting Started Guide, section 2.3 "Flash memory programming" for more information. Users should ensure these do not overlap with any other entries in the file.

Addresses in this file are expressed as an offset from the base address of the flash (that is, 0x08000000).

```

NOR10UPDATE: AUTO

; Image Update:NONE/AUTO/FORCE

NOR10ADDRESS: 0x00400000

; Image Flash Address

NOR10FILE: \SOFTWARE\fwu_fip.bin

; Image File Name

NOR10LOAD: 00000000

; Image Load Address

NOR10ENTRY: 00000000

; Image Entry Point

NOR11UPDATE: AUTO

; Image Update:NONE/AUTO/FORCE

NOR11ADDRESS: 0x03EB8000

; Image Flash Address

; Image File Name

NOR11FILE: \SOFTWARE\ns_bl1u.bin

NOR11LOAD: 00000000

; Image Load Address

; Image Load Address

NOR11ENTRY: 00000000

NOR12UPDATE: AUTO

; Image Update:NONE/AUTO/FORCE

NOR12ADDRESS: 0x01000000

; Image Flash Address

NOR12FILE: \SOFTWARE\backup_fip.bin

; Image File Name

NOR12LOAD: 00000000

; Image Load Address

NOR12ENTRY: 00000000

; Image Entry Point

```

Copyright (c) 2019, Arm Limited. All rights reserved.

This document describes how to build the Trusted Firmware-A Tests (TF-A Tests) and run them on a set of platforms. It assumes that the reader has previous experience building and running Trusted Firmware-A (TF-A).

Copyright (c) 2019-2020, Arm Limited. All rights reserved.

**CHAPTER**

THREE

# **PROCESSES & POLICIES**

# 3.1 Checking source code style

When making changes to the source for submission to the project, the source must be in compliance with the Linux style guide. To assist with this, the project Makefile provides two targets, which both utilise the checkpatch.pl script that ships with the Linux source tree.

To check the entire source tree, you must first download copies of checkpatch.pl, spelling.txt and const\_structs.checkpatch available in the Linux master tree scripts directory, then set the CHECKPATCH environment variable to point to checkpatch.pl (with the other 2 files in the same directory).

Then use the following command:

make CHECKPATCH=<path-to-linux>/linux/scripts/checkpatch.pl checkcodebase

To limit the coding style checks to your local changes, use:

make CHECKPATCH=<path-to-linux>/linux/scripts/checkpatch.pl checkpatch

By default, this will check all patches between origin/master and your local branch. If you wish to use a different reference commit, this can be specified using the BASE\_COMMIT variable.

Copyright (c) 2019, Arm Limited. All rights reserved.

Copyright (c) 2019, Arm Limited. All rights reserved.

### FRAMEWORK DESIGN

This document provides some details about the internals of the TF-A Tests design. It is incomplete at the moment.

# 4.1 High-Level Behaviour

The EL3 firmware is expected to hand over to the TF-A tests with all secondary cores powered down, i.e. only the primary core should enter the TF-A tests.

The primary CPU initialises the platform and the TF-A tests internal data structures.

Then the test session begins. The TF-A tests are executed one after the other. Tests results are saved in non-volatile memory as we go along.

Once all tests have completed, a report is printed over the serial console.

#### 4.2 Global Code Structure

The code is organised into the following categories (present as directories at the top level or under the tftf/directory):

#### · Drivers.

Some examples follow, this list might not be exhaustive.

- Generic GIC driver.

- arm\_gic.h contains the public APIs that tests might use. Both GIC architecture versions 2 and 3 are supported.

- PL011 UART driver.

- VExpress NOR flash driver.

Note that tests are not expected to use this driver in most cases. Instead, they should use the tftf\_nvm\_read() and tftf\_nvm\_write() wrapper APIs. See definitions in tftf/framework/include/nvm.h. See also the NVM validation test cases (tftf/tests/framework\_validation\_tests/test\_validation\_nvm.c) for an example of usage of these functions.

- SP805 watchdog.

Used solely to generate an interrupt that will reset the system on purpose (used in tftf\_plat\_reset()).

- SP804 timer.

This is used as the system timer on Juno. It is configured such that an interrupt is generated when it reaches 0. It is programmed in one-shot mode, i.e. it must be rearmed every time it reaches 0.

#### · Framework.

Core features of the test framework.

#### · Library code.

Firstly, there is include/libc/ which provides standard C library functions like memcpy(), printf() and so on. Additionally, various other APIs are provided under include/lib/. The below list gives some examples but might not be exhaustive.

#### - aarch64/

Architecture helper functions for e.g. system registers access, cache maintenance operations, MMU configuration, ...

#### - events.h

Events API. Used to create synchronisation points between CPUs in tests.

#### - irq.h

IRQ handling support. Used to configure IRQs and register/unregister handlers called upon reception of a specific IRQ.

#### power\_management.h

Power management operations (CPU ON/OFF, CPU suspend, etc.).

#### - sgi.h

Software Generated Interrupt support. Used as an inter-CPU communication mechanism.

#### - spinlock.h

Lightweight implementation of synchronisation locks. Used to prevent concurrent accesses to shared data structures.

#### - timer.h

Support for programming the timer. Any timer which is in the *always-on* power domain can be used to exit CPUs from suspend state.

#### - tftf\_lib.h

Miscellaneous helper functions/macros: MP-safe printf(), low-level PSCI wrappers, insertion of delays, raw SMC interface, support for writing a string in the test report, macros to skip tests on platforms that do not meet topology requirements, etc.

#### - io\_storage.h

Low-level IO operations. Tests are not expected to use these APIs directly. They should use higher-level APIs like tftf\_nvm\_read() and tftf\_nvm\_write().

#### · Platform specific.

Note that include/plat/common/plat\_topology.h provides the interfaces that a platform must implement to support topology discovery (i.e. how many CPUs and clusters there are).

#### · Tests.

The tests are divided into the following categories (present as directories in the tftf/tests/ directory):

# - Framework validation tests.

Tests that exercise the core features of the framework. Verify that the test framework itself works properly.

#### - Runtime services tests.

Tests that exercise the runtime services offered by the EL3 Firmware to the Normal World software. For example, this includes tests for the Standard Service (to which PSCI belongs to), the Trusted OS service or the SiP service.

#### - CPU extensions tests.

Tests some CPU extensions features. For example, the AMU tests ensure that the counters provided by the Activity Monitor Unit are behaving correctly.

#### - Firmware Update tests.

Tests that exercise the Firmware Update feature of TF-A.

#### - Template tests.

Sample test code showing how to write tests in practice. Serves as documentation.

#### - Performance tests.

Simple tests measuring the latency of an SMC call.

#### - Miscellaneous tests.

Tests for RAS support, correct system setup, ...

All assembler files have the .S extension. The linker source file has the extension .ld.S. This is processed by GCC to create the linker script which has the extension .ld.

### 4.3 Detailed Code Structure

The cold boot entry point is tftf\_entrypoint (see tftf/framework/aarch64/entrypoint.S). As explained in *High-Level Behaviour*, only the primary CPU is expected to execute this code.

Tests can power on other CPUs using the function tftf\_cpu\_on(). This uses the PSCI CPU\_ON API of the EL3 Firmware. When entering the Normal World, execution starts at the warm boot entry point, which is tftf\_hotplug\_entry() (see tftf/framework/aarch64/entrypoint.S).

Information about the progression of the test session and tests results are written into Non-Volatile Memory as we go along. This consists of the following data (see struct tftf\_state\_t typedef in tftf/framework/include/nvm.h):

• test\_to\_run

Reference to the test to run.

• test\_progress

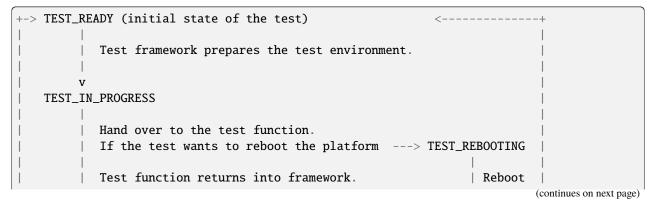

Progress in the execution of test\_to\_run. This is used to implement the following state machine:

(continued from previous page)

• testcase\_buffer

A buffer that the test can use as a scratch area for whatever it is doing.

- testcase\_results

- result\_buffer\_size

- result\_buffer

Buffer holding the tests output. Tests output are concatenated.

# 4.4 Interrupt Management

The TF-A tests expect SGIs #0 to #7 to be available for their own usage. In particular, this means that Trusted World software must configure them as non-secure interrupts.

SGI #7 has a special status. It is the SGI that the timer management framework sends to all CPUs when the system timer fires off (see the definition of the constant IRQ\_WAKE\_SGI in the header file include/lib/irq.h). Although test cases can use this specific SGI - e.g. they can register an IRQ handler for it and use it as an inter-CPU communication mechanism - they have to be aware of the underlying consequences. Some tests, like the PSCI CPU\_SUSPEND tests, rely on this SGI to be enabled in order to wake up CPUs from their suspend state. If it is disabled, these tests will leave the system in an unresponsive state.

Copyright (c) 2018-2019, Arm Limited. All rights reserved.

**CHAPTER**

**FIVE**

# IMPLEMENTING TESTS

This document aims at providing some pointers to help implementing new tests in the TFTF image.

### 5.1 Test Structure

A test might be divided into 3 logical parts, detailed in the following sections.

### 5.1.1 Prologue

A test has a main entry point function, whose type is:

```

typedef test_result_t (*test_function_t)(void);

```

See tftf/framework/include/tftf.h.

Only the primary CPU enters this function, while other CPUs are powered down.

First of all, the test function should check whether this test is applicable to this platform and environment. Some tests rely on specific hardware features or firmware capabilities to be present. If these are not available, the test should be skipped. For example, a multi-core test requires at least 2 CPUs to run. Macros and functions are provided in include/common/test\_helpers.h to help test code verify that their requirements are met.

#### 5.1.2 Core

This is completely dependent on the purpose of the test. The paragraphs below just provide some useful, general information.

The primary CPU may power on other CPUs by calling the function  $tftf_cpu_on()$ . It provides an address to which secondary CPUs should jump to once they have been initialized by the test framework. This address should be different from the primary CPU test function.

Synchronization primitives are provided in include/lib/events.h in case CPUs' execution threads need to be synchronized. Most multi-processing tests will need some synchronisation points that all/some CPUs need to reach before test execution may continue.

Any CPU that is involved in a test must return from its test function. Failure to do so will put the framework in an unrecoverable state, see the *Change Log & Release Notes* for details on this and other known limitations. The return code indicates the test result from the point of view of this CPU. At the end of the test, individual CPU results are aggregated and the overall test result is derived from that. A test is considered as passed if all involved CPUs reported a success status code.

# 5.1.3 Epilogue

Each test is responsible for releasing any allocated resources and putting the system back in a clean state when it finishes. Any change to the system configuration (e.g. MMU setup, GIC configuration, system registers, ...) must be undone and the original configuration must be restored. This guarantees that the next test is not affected by the actions of the previous one.

One exception to this rule is that CPUs powered on as part of a test must not be powered down. As already stated above, as soon as a CPU enters the test, the framework expects it to return from the test.

# 5.2 Template Test Code

Some template test code is provided in tftf/tests/template\_tests. It can be used as a starting point for developing new tests. Template code for both single-core and multi-core tests is provided.

# 5.3 Build System Integration

All test code is located under the tftf/tests directory. Tests are usually divided into categories represented as sub-directories under tftf/tests/.

The source file implementing the new test code should be added to the appropriate tests makefile, see .\*mk files under tftf/tests.

The new test code should also appear in a tests manifest, see \*.xml files under tftf/tests. A unique name and test function must be provided. An optional description may be provided as well.

For example, to create a test case named "Foo test case", whose test function is foo(), add the following line in the tests manifest:

```

<testcase name="Foo test case" function="foo" />

```

A testcase must be part of a testsuite. The testcase XML node above must be inside a testsuite XML node. A unique name and a description must be provided for the testsuite.

For example, to create a test suite named "Bar test suite", whose description is: "An example test suite", add the following 2 lines:

```

<testsuite name="Bar test suite" description="An example test suite">

</testsuite>

```

See the template test manifest for reference: tftf/tests/tests-template.xml.

Copyright (c) 2018-2020, Arm Limited. All rights reserved.

**CHAPTER**

SIX

# **PORTING**

# **6.1 Platform Requirements**

The TF-A Tests rely on the following features to be present on the platform and accessible from Normal World.

- Watchdog

- Non-Volatile Memory

- · System Timer

This also means that a platform port of the TF-A Tests must include software drivers for those features.

Copyright (c) 2019, Arm Limited. All rights reserved.

# **6.2 Storage Abstraction Layer**

In order to improve platform independence and portability a storage abstraction layer is used to store test results to non-volatile platform storage.

Each platform should register devices and their drivers via the storage layer. These drivers then need to be initialized using the tftf\_platform\_setup() function.

Warning: It is mandatory to implement at least one storage driver.

For the FVP and Juno platforms the NOR Flash driver is provided as the default means to store test results to storage. The storage layer is described in the header file include/lib/io\_storage.h. The implementation of the common library is in drivers/io/io\_storage.c and the driver files are located in drivers/io/.

Copyright (c) 2019, Arm Limited. All rights reserved.

# 6.3 Build Flags

The platform may define build flagsto to control inclusion or exclusion of certain tests. These flags must be defined in the platform makefile which is included by the build system.

#### PLAT TESTS SKIP LIST

This build flag can be defined by the platform to control exclusion of some testcases from the default test plan for a platform. If used this needs to point to a text file which follows the following criteria:

- Contain a list of tests to skip for this platform.

- Specify 1 test per line, using the following format:

```

testsuite_name/testcase_name

```

where testsuite\_name and testcase\_name are the names that appear in the XML tests file.

• Alternatively, it is possible to disable a test suite entirely, which will disable all test cases part of this test suite. To do so, only specify the test suite name, omitting the /testcase\_name part.

Copyright (c) 2019, Arm Limited. All rights reserved.

# **6.4 Mandatory Modifications**

# 6.4.1 File: platform\_def.h

Each platform must ensure that a header file of this name is in the system include path with the following constants defined. This may require updating the list of PLAT\_INCLUDES in the platform.mk file. In the ARM FVP port, this file is found in plat/arm/board/fvp/include/platform\_def.h.

#### • #define : PLATFORM\_LINKER\_FORMAT

Defines the linker format used by the platform, for example elf64-littleaarch64 used by the FVP.

#### • #define : PLATFORM\_LINKER\_ARCH

Defines the processor architecture for the linker by the platform, for example *aarch64* used by the FVP.

#### • #define : PLATFORM STACK SIZE

Defines the stack memory available to each CPU. This constant is used by plat/common/aarch64/platform\_mp\_stack.S.

### • #define : PLATFORM\_CLUSTER\_COUNT

Defines the total number of clusters implemented by the platform in the system.

#### • #define : PLATFORM\_CORE\_COUNT

Defines the total number of CPUs implemented by the platform across all clusters in the system.

#### • #define : PLATFORM\_NUM\_AFFS

Defines the total number of nodes in the affinity hierarchy at all affinity levels used by the platform.

#### • #define : PLATFORM\_MAX\_AFFLVL

Defines the maximum number of affinity levels in the system that the platform implements. ARMv8-A has support for 4 affinity levels. It is likely that hardware will implement fewer affinity levels. For example, the Base

26 Chapter 6. Porting

AEM FVP implements two clusters with a configurable number of CPUs. It reports the maximum affinity level as 1.

#### • #define : PLAT MAX SPI OFFSET ID

Defines the offset of the last Shared Peripheral Interrupt supported by the TF-A Tests on this platform. SPI numbers are mapped onto GIC interrupt IDs, starting from interrupt ID 32. In other words, this offset ID corresponds to the last SPI number, to which 32 must be added to get the corresponding last GIC IRQ ID.

E.g. If PLAT\_MAX\_SPI\_OFFSET\_ID is 10, this means that IRQ #42 is the last SPI.

#### • #define : PLAT\_LOCAL\_PSTATE\_WIDTH

Defines the bit-field width of the local state in State-ID field of the power-state parameter. This macro will be used to compose the State-ID field given the local power state at different affinity levels.

#### • #define : PLAT\_MAX\_PWR\_STATES\_PER\_LVL

Defines the maximum number of power states at a power domain level for the platform. This macro will be used by the PSCI\_STAT\_COUNT/RESIDENCY tests to determine the size of the array to allocate for storing the statistics.

#### • #define : TFTF\_BASE

Defines the base address of the TFTF binary in DRAM. Used by the linker script to link the image at the right address. Must be aligned on a page-size boundary.

#### • #define : IRQ\_PCPU\_NS\_TIMER

Defines the IRQ ID of the per-CPU Non-Secure timer of the platform.

#### #define : IRQ CNTPSIRQ1

Defines the IRQ ID of the System timer of the platform.

#### • #define : TFTF\_NVM\_OFFSET

The TFTF needs some Non-Volatile Memory to store persistent data. This defines the offset from the beginning of this memory that the TFTF can use.

#### • #define : TFTF\_NVM\_SIZE

Defines the size of the Non-Volatile Memory allocated for TFTF usage.

If the platform port uses the ARM Watchdog Module (SP805) peripheral, the following constant needs to be defined:

#### • #define: SP805 WDOG BASE

Defines the base address of the SP805 watchdog peripheral.

If the platform port uses the IO storage framework, the following constants must also be defined:

#### #define : MAX\_IO\_DEVICES

Defines the maximum number of registered IO devices. Attempting to register more devices than this value using io\_register\_device() will fail with IO\_RESOURCES\_EXHAUSTED.

#### • #define : MAX\_IO\_HANDLES

Defines the maximum number of open IO handles. Attempting to open more IO entities than this value using io\_open() will fail with IO\_RESOURCES\_EXHAUSTED.

If the platform port uses the VExpress NOR flash driver (see drivers/io/vexpress\_nor/), the following constants must also be defined:

#### • #define: NOR FLASH BLOCK SIZE

Defines the largest block size as seen by the software while writing to NOR flash.

# 6.4.2 Function : tftf\_plat\_arch\_setup()

```

Argument : void

Return : void

```

This function performs any platform-specific and architectural setup that the platform requires.

In both the ARM FVP and Juno ports, this function configures and enables the MMU.

### 6.4.3 Function: tftf early platform setup()

```

Argument : void

Return : void

```

This function executes with the MMU and data caches disabled. It is only called by the primary CPU. It is used to perform platform-specific actions very early in the boot.

In both the ARM FVP and Juno ports, this function configures the console.

# 6.4.4 Function : tftf\_platform\_setup()

```

Argument : void

Return : void

```

This function executes with the MMU and data caches enabled. It is responsible for performing any remaining platform-specific setup that can occur after the MMU and data cache have been enabled.

This function is also responsible for initializing the storage abstraction layer used to access non-volatile memory for permanent storage of test results. It also initialises the GIC and detects the platform topology using platform-specific means.

### 6.4.5 Function: plat get nvm handle()

```

Argument : uintptr_t *

Return : void

```

It is needed if the platform port uses IO storage framework. This function is responsible for getting the pointer to the initialised non-volatile memory entity.

# 6.4.6 Function: tftf plat get pwr domain tree desc()

```

Argument : void

Return : const unsigned char *

```

This function returns the platform topology description array in a suitable format as expected by TFTF. The size of the array is expected to be PLATFORM\_NUM\_AFFS - PLATFORM\_CORE\_COUNT + 1. The format used to describe this array is:

1. The first entry in the array specifies the number of power domains at the highest power level implemented in the platform. This caters for platforms where the power domain tree does not have a single root node e.g. the FVP which has two cluster power domains at the highest level (that is, 1).

28 Chapter 6. Porting

2. Each subsequent entry corresponds to a power domain and contains the number of power domains that are its direct children.

The array format is the same as the one used by Trusted Firmware-A and more details of its description can be found in the Trusted Firmware-A documentation.

# 6.4.7 Function: tftf\_plat\_get\_mpidr()

```

Argument : unsigned int

Return : uint64_t

```

This function converts a given *core\_pos* into a valid MPIDR if the CPU is present in the platform. The *core\_pos* is a unique number less than the PLATFORM\_CORE\_COUNT returned by platform\_get\_core\_pos() for a given CPU. This API is used by the topology framework in TFTF to query the presence of a CPU and, if present, returns the corresponding MPIDR for it. If the CPU referred to by the *core\_pos* is absent, then this function returns INVALID\_MPID.

# 6.4.8 Function: plat\_get\_state\_prop()

```

Argument : unsigned int

Return : const plat_state_prop_t *

```

This functions returns the plat\_state\_prop\_t array for all the valid low power states from platform for a specified affinity level and returns NULL for an invalid affinity level. The array is expected to be NULL-terminated. This function is expected to be used by tests that need to compose the power state parameter for use in PSCI\_CPU\_SUSPEND API or PSCI\_STAT/RESIDENCY API.

# 6.4.9 Function: plat\_fwu\_io\_setup()

```

Argument : void

Return : void

```

This function initializes the IO system used by the firmware update.

# 6.4.10 Function : plat\_arm\_gic\_init()

```

Argument : void

Return : void

```

This function initializes the ARM Generic Interrupt Controller (GIC).

# 6.4.11 Function : platform\_get\_core\_pos()

```

Argument : u_register_t

Return : unsigned int

```

This function returns a linear core ID from a MPID.

# 6.4.12 Function: plat crash console init()

```

Argument : void

Return : int

```

This function initializes a platform-specific console for crash reporting.

# 6.4.13 Function : plat\_crash\_console\_putc()

```

Argument : int

Return : int

```

This function prints a character on the platform-specific crash console.

# 6.4.14 Function: plat crash console flush()

```

Argument : void

Return : int

```

This function waits until all the characters of the platform-specific crash console have been actually printed.

Copyright (c) 2019, Arm Limited. All rights reserved.

# **6.5 Optional Modifications**

The following are helper functions implemented by the test framework that perform common platform-specific tasks. A platform may choose to override these definitions.

# 6.5.1 Function: platform\_get\_stack()

```

Argument : unsigned long

Return : unsigned long

```

This function returns the base address of the memory stack that has been allocated for the CPU specified by MPIDR. The size of the stack allocated to each CPU is specified by the platform defined constant PLATFORM\_STACK\_SIZE.

Common implementation of this function is provided in plat/common/aarch64/platform\_mp\_stack.S.

30 Chapter 6. Porting

# 6.5.2 Function: tftf platform end()

Argument : void Return : void

This function performs any operation required by the platform to properly finish the test session.

The default implementation sends an EOT (End Of Transmission) character on the UART. This can be used to automatically shutdown the FVP models. When running on real hardware, the UART output may be parsed by an external tool looking for this character and rebooting the platform for example.

# 6.5.3 Function : tftf\_plat\_reset()

Argument : void Return : void

This function resets the platform.

The default implementation uses the ARM watchdog peripheral (SP805) to generate a watchdog timeout interrupt. This interrupt remains deliberately unserviced, which eventually asserts the reset signal.

Copyright (c) 2019, Arm Limited. All rights reserved.

Porting the TF-A Tests to a new platform involves making some mandatory and optional modifications for both the cold and warm boot paths. Modifications consist of:

- Implementing a platform-specific function or variable,

- · Setting up the execution context in a certain way, or

- Defining certain constants (for example #defines).

The platform-specific functions and variables are all declared in include/plat/common/platform.h. The framework provides a default implementation of variables and functions to fulfill the optional requirements. These implementations are all weakly defined; they are provided to ease the porting effort. Each platform port can override them with its own implementation if the default implementation is inadequate.

Copyright (c) 2019, Arm Limited. All rights reserved.

32 Chapter 6. Porting

## **CHANGE LOG & RELEASE NOTES**

Please note that the Trusted Firmware-A Tests version follows the Trusted Firmware-A version for simplicity. At any point in time, TF-A Tests version *x.y.* aims at testing TF-A version *x.y.* Different versions of TF-A and TF-A Tests are not guaranteed to be compatible. This also means that a version upgrade on the TF-A-Tests side might not necessarily introduce any new feature.

## 7.1 Version 2.9

## 7.1.1 New features

- More tests are made available in this release to help validate the functionalities in the following areas:

- FF-A Features

- Realm Management Extension

- New Architecture Specific features related to v8.8

- New platform ports

## **TFTF**

- FF-A testing:

- Reordered logs in the memory sharing tests.

- Memory share bumped to v1.1 EAC0.

- Updated tests for FFA\_FEATURES(FFA\_MEM\_RETRIEVE\_REQ).

- Fixed issues with RXTX buffer unmapping and dependencies on tests.

- Added check for execution state property of partitions.

- New tests:

- Tests for Errata management firmware interface.

- Ensure FPU state registers context is preserved in RL/SE/NS.

- Modified FEAT\_HCX test to also check for HCRX\_EL2 init value.

- Added basic SME2 tests.

- PSCI tests for OS-initiated mode.

- Added "nop" test to be used in conjunction with TFX.

- Introduced capability to generate Sync External Aborts (EA) in TFTF.

- New test to generate an SError.

- Tests to check whether the PMU is functional and if the state is preserved when switching worlds. PMEV-TYPER.evtCount width extended.

- Added support for more SPE versions.

- Platforms:

- RD-N2-Cfg3:

- \* Added TFTF support.

- · Miscellaneous:

- SIMD/FPU save/restore routine moved to common lib.

- Updated toolchain requirements documentation.

- Update SME/Mortlach tests.

- Unified Firmware First handling of lower EL EA.

- Moved trusted wdog API to spm\_common.

- Added the ability to skip tests for AArch32.

- Added config file to allow doc defaults be changed.

- Modified tests for FEAT RNG TRAP.

- Moved 'Stress test timer framework' to a new test suite 'tests-timer-stress'.

- Support for new binutils versions.

- Removed deprecated SPM libs and test code.

## **Realm Management Extension (RME)**

- Added helper macro for RME tests.

- Test Secure interrupt can preempt Realm EL1.

- Added PMU Realm tests.

- Added BP\_OPTION to REALM\_CFLAGS to allow build realm payload with BTI/Pauth support.

- Fixed build issues introduced by the TFTF Realm extension enhancement tests.

- Test case return codes updated according to RMM Bet0 specification.

- Fixed build problem related to rmi\_rec\_enter verbose log.

- Added randomization of SMC RMI commands parameters and checking of X4-X7 return values as per SMCCC v1.2.

## Cactus (Secure-EL1 test partition)

- Use of FFA\_CONSOLE\_LOG for debug logs.

- Test for consecutive same memory donation to other partitions.

- Now validating NWd can't share forbidden addresses.

- Support for registering irq handlers.

- Fixed attributes for NS memory region.

- · Removal of memory regions not page-aligned.

- Added check for core linear id matching id passed by SPMC.

### 7.1.2 Issues resolved since last release

- Build issue for older toolchains and other failures resolved.

- Dropped invalid access test from CI.

- Now checking that the PMU is supported before using any of it.

- Use of write instead of read to generate an SError to avoid sync exceptions instead.

- Fixed broken link to TRNG\_FW documentation.

- INIT\_TFTF\_MAILBOX() is called first for the invalid access test.

## 7.2 Version 2.8

## 7.2.1 New features

- More tests are made available in this release to help validate the functionalities in the following areas:

- FF-A Features

- Realm Management Extension

- New Architecture Specific features related to v8.8

- New platform ports

### **TFTF**

- FF-A testing:

- UUID included in partition information descriptors.

- Checks for size of partition information descriptors.

- Renamed FFA\_MSG\_RUN ABI function to FFA\_RUN and allowed it to return from Waiting state.

- Made ffa\_tests available for Ivy.

- Updated verbose message log structure.

- Prevented generate\_json.sh from being called more than once by requiring a list of partitions to be supplied.

- Added a temporary workaround for unexpected affinity info state to prevent a system panic.

7.2. Version 2.8 35

- Added test to exercise FFA\_CONSOLE\_LOG ABI.

- FF-A v1.1 Secure interrupts

- \* Added managed exit to first and second SP in call chain.

- \* Added test to exercise managed exit by two SPs in a call chain.

- \* Added tests to exercise NS interrupt being queued and signaled to SP.

### • New tests:

- Tests for SVE operations in Normal World and discover SVE vector length.

- Added cleanup TRNG service tests.

- Added test for SMCCC\_ARCH\_WORKAROUND\_3.

- Updated PAuth helpers to support QARMA3 algorithm.

- Added tests for RNG\_TRAP.

## • Platforms:

- SGI:

- \* Introduced platform variant build option.

- \* Re-organized header files.

- \* Migrated to secure uart port for routing tftf logs.

- N1SDP:

- \* Added TFTF support for N1SDP.

- RD-N2:

- \* Added TFTF support for RD-N2.

- RD-N2-Cfg1:

- \* Added TFTF support for RD-N2-Cfg1.

- RD-V1:

- \* Added TFTF support for RD-V1.

### · Miscellaneous:

- Added a missing ISB instruction in SME test.

- Refactor to make some helper functions re-usable.

- Updated build command to clean EL3 payload image.

- Move renaming of the primary dts file for ivy partitions.

- Added check that verifies if a platform supports el3\_payload before building it.

- Updated memory share test to meet Hafnium specification.

- Updated toolchain requirements documentation.

## Realm Management Extension (RME)

- Added Realm payload management capabilities to TFTF to act as a NS Host.

- Added test to verify that RMM and SPM can co-exist and work properly.

- Added function to reset delegated buffers to non-delegated state.

- Re-used existing wait\_for\_non\_lead\_cpus() function helper.

- Refactored RMI FID macros to simplify usage.

- · Added userguide for realm payload testing.

## Cactus (Secure-EL1 test partition)

- Corrected some tests message types from ERROR to VERBOSE.

- Increased the cactus number of xlat to allow the use of 48b PA size for memory sharing between SPs.

- Introduced a new direct request message command to resume after managed exit.

- Skip enabling virtual maintenance interrupts explicitly.

- Allowed sender to resume interrupted target vCPU.

- Added support for handling managed exit through vIRQ.

- Added support for discovering interrupt IDs of managed exit signals.

- Specified action in response to NS interrupt in manifest.

### Ivy (Secure-EL0 test partition)

- Allowed testing using VHE.

- Allowed Ivy partitions to use ffa\_helpers functions.

- Requirement of common name for Ivy partitions for consistency.

- Specified action in response to NS interrupt in manifest.

## 7.2.2 Issues resolved since last release

- Fixed SME header guard name.

- Fixed response for incorrect direct message request for FF-A.

## 7.3 Version 2.7

### 7.3.1 New features

- More tests are made available in this release to help validate the functionalities in the following areas:

- FF-A Features

- New Architecture Specific features related to v8.7

- New platform port

7.3. Version 2.7 37

### **TFTF**

- FF-A testing:

- FF-A partition information structure is updated to include UUIDs.

- Memory Management helper functions are refactored to fetch the details of smc call failures in tftf and cactus.

- Added test to validate memory sharing operations from SP to NS-endpoint are denied by SPMC.

- Added test to ensure an endpoint that sets its version to v1.0 receives v1.0 partition information descriptors as defined in v1.0 FF-A specification.

- Added test to validate that memory is cleared on memory sharing operations between normal world and secure world.

- FF-A v1.1 Secure interrupts

- \* Added support to enhance the secure interrupt handling test.

- \* Support for registering and unregistering custom handler that is invoked by SP at the tail end of the virtual interrupt processing.

- \* Added support for querying the ID of the last serviced virtual interrupt.

### • New tests:

- Added test to validate that realm region access is being prevented from normal world.

- Added test to validate that secure region access is being prevented from normal world.

- Added test to validate that secure region access is being prevented from realm world.

- Added test to validate that root region access is being prevented from realm world.

- Added a test for v8.7 Advanced floating-point behavior (FEAT AFP).

- Added a SPE test that reads static profiling system registers of available SPE version i.e. FEAT\_SPE/FEAT\_SPEv1p1/FEAT\_SPEv1p2.

- Added a test to validate functionality of WFET and WFIT instructions introduced by v8.7 FEAT\_WFxT.

- Added basic SME tests to ensure feature enablement by EL3 is proper for its usage at lower non-secure ELs.

- Added test to check Data Independent timing (DIT) field of PSTATE is retained on exception.

- Added test to ensure that EL3 has properly enabled access to FEAT\_BRBE from non-secure ELs.

#### • Platforms:

- Add initial platform support for corstone 1000.

- TC:

- \* Support for notification in tertiary SP manifest.

- FVP:

- \* Support to provide test memory addresses to validate the invalid memory access test from tftf(ns-el2).

- · Miscellaneous:

- Added support to configure the physical/virtual address space for FVP.

- Added common header file for defining macros with size to support all the platforms.

- Introduced handler for synchronous exceptions (AArch64).

- Added macros to extract the ISS portion of an ELx ESR exception syndrome register.

- Support to dynamically map/unmap test region to validate invalid memory access tests.

- Added support to receive boot information through secure partitions, according to the FF-A v1.1 EACO specification.

- Added an helper API function from SPM test suite to initialize FFA-mailbox and enable FF-A based message with SP.

- Updated the build string to display the rc-tagged version.

## Cactus (Secure-EL1 test partition)

- Added test for nonsecure memory sharing between Secure Partitions(SPs).

- Added test to validate that a realm region cannot be accessed from secure world.

- Added test to permit checking a root region cannot be accessed from secure world.

- Extended the test command CACTUS\_MEM\_SEND\_CMD to add support for memory sharing flags.

- Added support to save the state of general purpose registers x0-x4 at the entry to cold boot and restore them before jumping to entrypoint of cactus.

## 7.3.2 Issues resolved since last release

- Fixed a bug to align RMI FIDs with SMCCC.

- Fixed encoding of vCPU and receiver IDs in the FFA\_NOTIFICATION\_GET interface to comply with the FF-A v1.1 beta0 specification.

- Fixed memory retrieve request attributes by enforcing them to be inner shareable rather than outer.

- Fixed static memory mapping of EL3 in EL2.

- Fixed a spurious error log message with memory share test.

- Aligning RMI FIDs with SMCCC.

- Fixed PSCI system suspend test suite execution in a four world system.

- Configured the build system to use DWARF 4 standard for debug builds with ArmDS.

- Introduced macro IRQ\_TWDOG\_INTID for the Tegra210, Tegra186 and Tegra194 platforms to fix the compilation failures.

## 7.4 Version 2.6

### 7.4.1 New features

- More tests are made available in this release to help validate the functionalities in the following areas:

- Firmware Framework for Arm A-profile(FF-A)

- Realm Management Extensions(RME)

- Embedded Trace Extension and Trace Buffer Extension (ETE and TRBE)

7.4. Version 2.6 39

### **TFTF**

- FF-A testing:

- Update FF-A version to v1.1

- Added helpers for SPM tests to check partition info of SPs from normal world.

- Added tests to check for ffa\_features supported.

- Added test for FFA\_RXTX\_UNMAP ABI.

- Added test for FFA\_SPM\_ID\_GET.

- FF-A v1.1 Notifications

- \* Added test for notifications bitmap create and destroy ABIs.

- \* Added test for notifications set and get ABIs.

- \* Added test for notification INFO\_GET ABI.

- \* Added test to check notifications pending interrupt is injected into and handled by the expected vCPU in a MP setup.

- \* Added test for signaling from MP SP to UP SP.

- \* Added test to check notifications interrupt IDs retrieved with FFA\_FEATURES ABI.

- \* Added test to check functionality of notifications scheduled receiver interrupt.

- FF-A v1.1 Secure interrupts

- \* Added support for handling secure interrupts in Cactus SP.

- \* Added several tests to exercise secure interrupt handling while SP is in WAIT-ING/RUNNING/BLOCKED state.

### • New tests:

- Enabled SVE tests

- Added test for trace system registers access.

- Added test for trace filter control registers access.

- Added test for trace buffer control registers access.

- Added test to check PSTATE in SDEI handler.

- Added test to check if HCRX\_EL2 is accessible.

### • Platforms:

- TC0:

- \* Support for direct messaging with managed exit.

- \* Support for building S-EL0 Ivy partition.

- FVP:

- \* Update Cactus secure partitions to indicate Managed exit support.

- Miscellaneous

- Added random seed generation capability and ability to specify build parameters for SMC Fuzzer tool.

## Cactus (Secure-EL1 test partition)

- · Added helper for Cactus SP sleep.

- Added test commands to request use of notifications interfaces.

- Added several commands that generate direct message requests to assist in testing secure interrupt handling and notifications features in FF-A v1.1

- Added support for SP805 Trusted Watchdog module.

## Ivy (Secure-EL1 test partition)

- · Add shim layer to Ivy partition and enable PIE.

- Define Ivy partition manifest and use FF-A for message handling.

- Prepare S-EL1/0 environment for enabling S-EL0 application.

## Realm Management Extension(RME)

- Added tests to run RMI and SPM on multiple CPUs concurrently.

- Added tests for multi CPU delegation and fail conditions.

- Added tests to query RMI version on multiple CPUs.

### 7.4.2 Issues resolved since last release

- Fixed Ivy partition start address for TC0.

- Fixed SP manifests to use little endian format UUID.

- Fixed a bug in memory sharing test for Cactus SP.

- Invalidate data cache for NS\_BL1U and NS\_BL2U images.

- Fixed attributes to Read-Write only for memory regions described in partition manifests.

## 7.5 Version 2.5

## 7.5.1 New features

- More tests are made available in this release to help validate the functionalities in the following areas:

- True Random Number Generator (TRNG) test scenarios.

- Multicore / Power State Controller Interface (PSCI) tests.

- v8.6 Activity Monitors Unit (AMU) enhancements test scenarios.

- Secure Partition Manager (SPM) / Firmware Framework (FF-A) v1.0 testing.

- \* Interrupt Handling between Non-secure and Secure world.

- \* Direct messages and memory sharing between Secure Partitions(SP).

- \* Many tests to exercise FF-A v1.0 ABIs.

7.5. Version 2.5 41

\* SPM saving/restoring the NS SIMD context enabling a normal world FF-A endpoint (TFTF) and a secure partition to use SIMD vectors and instructions independently.

### **TFTF**

- SPM / FF-A v1.0 testing.

- Refactor FF-A memory sharing tests

- \* Created helper functions to initialize ffa\_memory\_region and to send the respective memory region to the SP, making it possible to reuse the logic in SP-to-SP memory share tests.

- \* Added comments to document relevant aspects about memory sharing.

- Trigger direct messaging between SPs.

- \* Use cactus command 'CACTUS\_REQ\_ECHO\_SEND\_CMD' to make cactus SPs communicate with each other using direct message interfaces.

- Added helpers for SPM tests.

- \* Checking SPMC has expected FFA\_VERSION.

- \* Checking that expected FF-A endpoints are deployed in the system.

- \* Getting global TFTF mailbox.

- Replace '.inst' AArch64 machine directives with CPU Memory Tagging Extension instructions in 'test mte instructions' function.

- Add build option for Arm Feature Modifiers.

- This patch adds a new ARM\_ARCH\_FEATURE build option to add support for compiler's feature modifiers.

- Enable 8 cores support for Theodul DSU(DynamIQ Shared Unit) for the Total Compute (TC0) platform.

- New tests:

- Remove redundant code and add better tests for TRNG SMCs.

- \* Tests that the Version, Features, and RND calls conform to the spec.

- New tests for v8.6 AMU enhancements (FEAT\_AMUv1p1)

- \* Make sure AMU offsets are being saved and restored properly.

- Tests to request SP-to-SP memory share.

- SP-to-SP direct messaging deadlock test.

- \* TFTF sends CACTUS\_REQ\_DEADLOCK\_CMD to cactus SP.

### Cactus(Secure-EL1 test partition)

- Enable managed exit for primary cactus secure partition.

- Helper commands needed for interrupt testing.

- Add handler from managed exit FIQ interrupt.

- Make ffa\_id global.

- Implement HF\_INTERRUPT\_ENABLE Hafnium hypervisor call wrapper. With this service, a secure partition calls into the SPMC to enable/disable a particular virtual interrupt.

- Invalidate the data cache for the cactus image.

- · Helper commands needed for interrupt testing.

- CACTUS\_SLEEP\_CMD & CACTUS\_INTERRUPT\_CMD added.

- Decouple exception handling from tftf framework.

- With new interrupt related tests coming up in Cactus, added separate exception handler code for irq/fiq in Cactus.

- Hypervisor calls moved to a separate module.

- Add secondary entry point register function.

- · Declare third SP instance as UP SP.

- Provision a cold boot path for secondary cores (or secondary pinned execution contexts).

- Tidy message loop, commands definitions, direct messaging API definitions.

- Helpers for error logging after FF-A calls.

- Properly placing Cactus test files.

- Tidying FF-A Memory Sharing tests.

- Use CACTUS\_ECHO\_CMD in direct message tests.

- · Refactor handling of commands.

- Added helper macros to define a command handler, build a command table in which each element

is a pair of the handler and respective command ID. Available tests have been moved to their own

command handler.

- · Extend arguments in commands responses.

- In the test commands framework, added template to extend number of values to include in a command response.

- · Check FF-A return is a valid direct response.

- Added a helper function to check if return of FFA\_MSG\_SEND\_DIRECT\_REQ is FFA\_MSG\_SEND\_DIRECT\_RESP.

- FFA\_MSG\_DIRECT\_RESP call extended to use 5 registers.

- Added accessors for arguments from FF-A calls.

- Some accessors for arguments from FF-A calls, namely for func id, error code, and direct message destination/source.

- Use virtual counter for sp sleep.

- Changes sp\_sleep() to use virtual counter instead of physical counter.

- Checks if SIMD vectors are preserved in the normal world while transitioning from normal world to secure world

and back to normal world.

- Tidying common code to tftf and cactus.

- Refactor cactus\_test\_cmds.h to incorporate static inline functions instead of macros to enforce type checking.

- Removed reference to Hafnium in name from helper function and macro to make them generic.

- For consistency added the cmd id 'CACTUS\_MEM\_SEND\_CMD'.

- Add command to request memory sharing between SPs.

7.5. Version 2.5 43